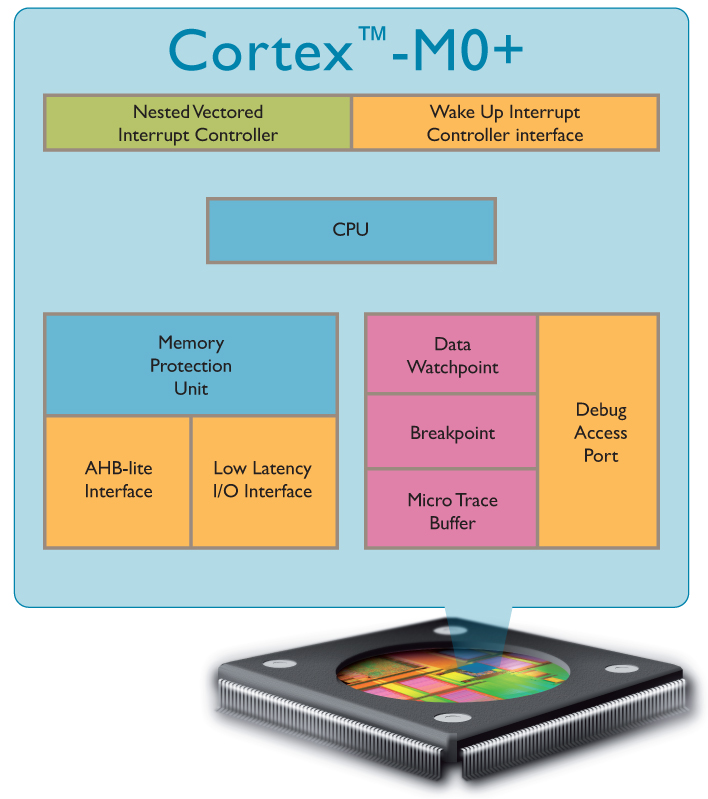

The ARM Cortex M0+ processor is the most energy efficient processor, the company’s target is low cost MCU, sensor and control markets. Apparently it seems that it will not easy at all but if the company strictly follow their success guideline then may be it possible. The Cortex M0+ processor comes with a wide selection of options to provide flexible development.

Why Cortex M0+?

- The most energy efficient ARM processor

An optimized architecture with a core pipeline of just two stages, enables the Cortex-M0+ processor to achieve a power consumption of just 11.2uW/MHz (90LP process, minimal configuration), while raising the performance to 1.77 CoreMark/MHz. - Simplicity

The Cortex-M0+ processor keeps the same 56 instructions of the Cortex-M0 processor, enabling simple and quick development. The Thumb instruction set offers an unrivaled code-density while providing access to 32-bit computation performance. The combination of the these features make the Cortex-M0+ processor a natural and cost effective successor to 8/16-bit devices in a wide variety of applications, while retaining tool and binary upwards compatibility with the feature-rich Cortex-M3 and Cortex-M4 processors. - Versatility

Each application is different and has its specific needs. To enable our Partners to design solutions fitting the widest range of applications, the Cortex-M0+ processor offers a wide choice of options. Many of these, such as the Memory Protection Unit and the relocatable vector-table are common to the Cortex-M3 and Cortex-M4 processors, while others have been specifically developed for this new processor, namely the single-cycle I/O interface for faster control and the Micro Trace Buffer for enhanced debug.

Specifications

| ARM Cortex-M0+ Features | |

| ISA Support | Thumb / Thumb-2 subset |

| Pipeline | 2 stage |

| Performance Efficiency |

1.77 CoreMark/MHz – 0.93 DMIPS/MHz (RVCT 5.0.90 compiler) |

| Memory Protection | Optional 8 region MPU with sub regions and background region |

| Interrupts | Non-maskable Interrupt (NMI) + 1 to 32 physical interrupts |

| Sleep Modes | Integrated WFI and WFE Instructions and Sleep On Exit capability. Sleep & Deep Sleep Signals. Optional Retention Mode with ARM Power Management Kit |

| Bit Manipulation | Bit banding region can be implemented with Cortex-M System Design Kit |

| Enhanced Instructions | Hardware single-cycle (32×32) multiply option |

| Debug | Optional JTAG & Serial-Wire Debug Ports. Up to 4 Breakpoints and 2 Watch points |

| Trace | Optional Micro Trace Buffer |

ARM Cortex-M Technologies

Each Cortex-M series processor delivers specific benefits, and all are underpinned by fundamental technologies that make Cortex-M processors ideal for a broad range of embedded applications.

RISC processor core

- High performance 32-bit CPU

- Deterministic operation

- Low latency 2-stage pipeline

Low power modes

- Integrated sleep state support

- Multiple power domains

- Architectural software control

Tools and RTOS support

- Broad 3rd party tools support

- Cortex Micro-controller Software Interface Standard (CMSIS)

- Maximizes software effort reuse

Nested Vectored Interrupt Controller (NVIC)

- Low latency, low jitter interrupt response

- No need for assembly programming

- Interrupt service routines in pure C

More Details Click.

Press Release

Source: ARM

[ttjad keyword=”processor”]